发射极耦合逻辑(ECL)作用特性_电路图_优缺点

发射极耦合逻辑(ECL)于1956年8月由Hannon S. Yourke在IBM首次发明。这种逻辑也称为电流模式逻辑,用于IBM 7090和7094计算机。与数字逻辑系列相比,ECL系列非常快。

通常情况下,发射极耦合逻辑系列提供小于1ns的传播延迟,是一个基于双极结型晶体管的逻辑系列,也是可用于设计传统逻辑系统的最快的逻辑系列电路。

基本概念

发射极耦合逻辑是传统逻辑系统设计中使用的最好的基于BJT的逻辑系列,有时也称为电流模式逻辑,是一种非常高速的数字技术。通常ECL被认为是最快的逻辑IC,它通过使用非常小的电压摆幅实现高速运行,同时避免晶体管进入饱和区。

发射极耦合逻辑的实现利用称为PECL(正参考ECL)的正电源电压。在早期的ECL门中,由于抗噪性而使用负电压电源。此后,与TTL逻辑系列相比,正参考ECL因其更兼容的逻辑电平而变得非常有名。

发射极耦合逻辑消耗大量静态功率,但是,与高频下的CMOS相比,其总电流消耗较低。因此,ECL主要有利于时钟分配电路和基于高频的应用。

功能作用

发射极耦合逻辑的特性将使它们用于许多基于高性能的应用程序。

- 提供两个始终互补的输出,因为电路的操作基于差分放大器。

- 该逻辑系列主要适用于单片制造方法,因为逻辑电平是电阻比的函数。

- ECL系列的设备无需使用任何外部逆变器即可生成所建议功能的正确和互补输出。因此,它减少了封装数量和功率要求,还减少了因时间延迟而出现的问题。

- 差分放大器设计中的ECL器件提供了广泛的性能灵活性,因此ECL电路允许用作数字电路和线性电路。

- ECL Gate的设计具有常高低输入阻抗,非常有利于获得大扇出和驱动能力。

- ECL器件在电源上产生恒定电流消耗以简化电源设计。

- 包括发射极开路输出的ECL器件仅允许它们包含传输线驱动能力。

主要特性

ECL的特征包括以下内容。

- 与 TTL相比,ECL的传播时间更快,范围为0.5到2ns。但是,与30mW的TTL相比,发射极耦合逻辑功耗更高。

- ECL的I/O电压有一个小的摆动,即0.8。

- ECL输入阻抗高,输出阻抗低。因此,晶体管的状态变化非常快。

- ECL的扇出能力高,栅极延迟低。

- ECL的o/p逻辑从低状态变为高状态,但这些状态的电压水平将在TTL和EC之间变化。

- ECL的抗扰度为0.4V。

反相器应用电路

反相器的发射极耦合逻辑电路如下图所示,由电阻和晶体管设计而成。在该电路中,两个晶体管的发射极端子简单地连接到限流电阻RE,用于避免晶体管进入饱和。这里晶体管的输出取自集电极端子而不是发射极端子。该电路提供两个输出Vout(反相输出)和Vout2(非反相输出)和输入端,如Vin,其中给出了高或低输入。其中,+Vcc=5V。

上述发射极耦合逻辑的操作过程是,每当高电平输入提供给ECL电路时,它就会使“Q1”晶体管导通,使Q2晶体管关断,但Q1晶体管不会饱和。因此,这会将VOUT2输出拉至高电平,而VOUT1输出的值将由于R1内的压降而变为低电平。

同样,当提供给ECL的VIN值为LOW时,它会使Q1晶体管关闭和Q2晶体管导通。因此,Q2晶体管不会进入饱和状态。因此,由于R2电阻下降,VOUT1输出将被拉高,VOUT2输出将变低。

接下来看看晶体管Q1和Q2在施加电压时是如何开启和关闭的。

该电路中的两个晶体管(Q1和Q2)通过共发射极电阻连接为差分放大器。

此示例电路的电源电压为VCC=5.0、VBB=4.0和VEE=0V。输入高电平和低电平值简单地定义为4.4V和3.6V。实际上,该电路产生高出0.6伏的低输出和高电平。当然,这在实际ECL电路中会得到纠正。

一旦Vin为高电平,则Q1晶体管导通,但未饱和且Q2晶体管关闭。因此,像VOUT2这样的输出电压通过R2电阻被拉至5V,并且可以看出R1电阻两端的压降约为0.8V,因此VOUT1=4.2V(低)。此外,VE=VOUT1–VQ1=>4.2V – 0.4V=3.8V,因为晶体管Q1完全导通。

而一旦Vin为低电平,Q2晶体管将导通,但不会饱和,Q1晶体管将关闭。因此,使用R1电阻将VOUT1拉至5.0V,并且可以显示VOUT2为4.2V。此外,当晶体管Q2导通时,VE=>VOUT2– VQ2=>4.2V–0.8V=>3.4V。

在ECL中,两个晶体管永远不会饱和,因为输入/输出电压摆幅相当小,例如0.8v,而输入阻抗高,输出电阻低。这有助于ECL以更短的传播延迟时间更快地运行。

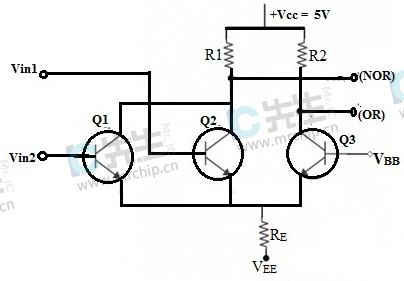

两个输入发射极耦合逻辑OR/NOR Gate电路

两个输入发射极耦合逻辑或/或非门电路如下图所示,该电路是对上述反相器电路进行改造设计而成。修改的是在输入端增加一个额外的晶体管。该电路的工作非常简单。当Q1和Q2晶体管的输入均为低电平时,将使输出 1 (Vout1) 变为高电平。所以,这个Vout1对应于NOR gate的输出。

如果Q3晶体管导通,则它会使第二个输出 (Vout2) 变为高电平。因此,此Vou2输出对应于或门输出。同样,如果Q1和Q2晶体管输入均为高电平,则它将打开Q1和Q2晶体管并在VOUT1端子提供低输出。

而如果Q3晶体管在整个操作过程中关闭,那么它将在VOUT2端子提供高输出。因此,OR门/NOR门的真值表如下所示:

| Inputs | Inputs | OR | NOR |

| A | B | Y | Y |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

优缺点

发射极耦合逻辑的主要优点包括以下几方面内容:

- ECL的扇出为25,与TTL相比更好,比CMOS还要低。

- ECL的平均传播延迟时间为1至4ns,优于CMOS、TTL,因此它被称为最快的逻辑系列。

- 当发射极耦合逻辑门中的BJT在有源区工作时,与所有逻辑系列相比,它们具有最大速度。

- ECL门生成互补输出。

- 电源引线中不存在电流开关尖峰。

- 输出可以联合耦合以提供线或功能。

- ECL参数随温度变化不大。

- 仅从一个芯片可访问的功能数量都很高。

发射极耦合逻辑的主要缺点包括以下几方面内容:

- 具有极小的噪声容限,即±200mV。

- 与其它逻辑门相比,功耗较高。

- 要与其他逻辑系列接口,需要电平转换器。

- 扇出限制容性负载。

- 与TTL相比,ECL门价格很昂贵。

- 与CMOS和TTL 相比,ECL抗噪能力最差。

主要应用

发射极耦合逻辑的应用包括以下几方面内容:

- 用作超高速通信设备(如光纤收发器接口、以太网和异步传输模式网络)中的逻辑和接口技术。

- 它是一个基于BJT逻辑系列,其高速运行可以通过使用相对较小的电压摆幅和避免晶体管进入饱和区来实现。

- 用于制作IBM 360/91内的ASLT电路。

- 通过在初级和次级晶体管之间使用单端偏置i/p和正反馈来获得反相器功能,从而避免使用堆叠晶体管。

- 用于超高速电子设备。

总结

以上就是关于发射极耦合逻辑简单内容概述,从上述内容可以了解到,与其它数字逻辑系列相比,发射极耦合逻辑是基于BJT的最快逻辑系列。此外,ECL通过使用小电压摆动并避免晶体管进入饱和区来实现其最大速度运行。该逻辑系列提供令人难以置信的1ns传播延迟,并且在最新的ECL系列中,该延迟还有所减少。