递增/递减计数器逻辑图_应用电路_优缺点

在数字逻辑和计算中,用于对脉冲进行计数的时序电路称为计数器。计数器是一组触发器,包括应用的CLK信号,这是触发器的广泛应用。这些被设计为单独的 IC(集成电路),以广泛用于数字电路和更大的IC。

计数器有不同类型,如约翰逊计数器、异步或纹波、同步计数器、十进制、环形计数器和递增/递减计数器。在本文中,小编介绍一种计数器类型,即递增/递减计数器的相关基础内容。

基本概念

递增/递减计数器也称为双向计数器,用于根据输入控制引脚的情况在任何方向上计数。在不同的应用中,这些计数器用于从零开始计数,以在达到固定值时提供输出条件内的变化;而其它计数器用于从固定值开始计数到零,以提供输出条件变化。

目前有一些类型的计数器,如TTL 74LS190和75LS191,它们可以根据递增/递减计数模式的输入引脚的条件在递增递减计数模式下工作。

应用电路

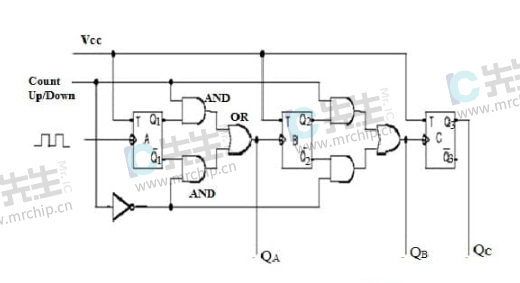

3位递增/递减计数器的电路图如下所示,该电路采用触发器设计。在递增计数器中,每一个触发器都是通过前一个触发器的正常o/p激活的(从主触发器的'Q'o/p到下一个触发器的CLK);而在递减计数器中,每个触发器都是通过前一个触发器的补码o/p激活的(从第一个触发器的输出到下一个触发器的CLK)。

这里递增/递减计数器的操作可以通过加减的控制输入来控制。此递增/递减计数器在两种模式下工作,如递增计数模式和倒计时模式。下面显示了计数和倒计时的逻辑图。

计时模式逻辑表格如下图所示:

| 状态 | QC | QB | QA |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 2 | 0 | 1 | 0 |

| 3 | 0 | 1 | 1 |

| 4 | 1 | 0 | 0 |

| 5 | 1 | 0 | 1 |

| 6 | 1 | 1 | 0 |

| 7 | 1 | 1 | 1 |

倒计时模式逻辑表格如下图所示:

| 状态 | QA | QB | QC |

| 7 | 1 | 1 | 1 |

| 6 | 1 | 1 | 0 |

| 5 | 1 | 0 | 1 |

| 4 | 1 | 0 | 0 |

| 3 | 0 | 1 | 1 |

| 2 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 |

众所周知,对于递增/递减计数的操作,有时前一个触发器需要从初级触发器的Q输出输入到下一个FF的CLK进行向上计数,有时需要从初级FF的Q^输出到CLK下一个触发器的递减计数。通常情况下,一个触发器可以容纳1位,因此对于三位操作,它需要3个触发器。

在上述电路中,在递增计数和递减计数两条控制线之间连接了一个反相器,以确保加计数和减计数不能同时处于高电平状态。

一旦递增或递减计数线保持高电平,则下方的与门将被禁用,因此它们的o/p将为零。因此,它们不会改变或门输出。同时将启用较高的与门。因此,'QA' 将提供整个或门以及进入B触发器的CLK输入。同样,“QB”将被选通到C触发器的CLK输入。因此,一旦应用输入信号,它就会向上计数并遵循从000 -111的正常二进制计数系列。

以同样的方式,一旦递增或递减计数线保持低电平,则上侧与门将被禁用,下侧与门将通过允许Q'A和Q'B在整个CLK中流动来启用FF的输入。因此,在这种状态下,当施加i/p脉冲时,该计数器将开始以递减模式计数。

时钟脉冲的计算

在递增计数器中,它从低到高开始计数,而在递减计数器中,它从高到低开始计数。在异步3位递增/递减计数器中,计数器输出取自触发器补码输出,如Q',而不是每个触发器的正常o/ps。起始计数系列是QA QB QC=>111。CLK“QA”的每个下降沿都会切换其条件。同样,对于QA'输出的每一次负转换,QB'输出都会切换,同样的事情也会发生在QC' 上。因此,计数系列继续从7减少到0,依此类推通过每个时钟脉冲。

在递增计数器中,每个触发器都是通过前一个触发器的正常o/p激活的(从初级触发器的'QA'o/p到下一个FF的CLK);而在递减计数器中,每个触发器都通过前一个 FF 的补码o/p激活(从第一个触发器QA'的输出到下一个触发器的CLK)。

在递增计数器中,第一个触发器连接到逻辑0,因此它会在每个下降沿触发。而第二个触发器的输入连接到第一个触发器的“QA”,然后一旦QA=1并且出现时钟下降沿,它就会改变其状态。

同样,第三个触发器连接到第二个触发器“QB”,然后当QB=1并且存在时钟下降沿时它会改变其状态。通过这个,可以产生递增计数器的计数状态。在每个第 8个下降沿之后,计数器将再次达到0 0 0状态。

在递减计数器中,第一个触发器连接到逻辑1,然后它会针对每个下降沿进行切换。第二个触发器的输入连接到第一个触发器QA',然后一旦QB'=1并且存在时钟下降沿,它就会改变其状态。

同样,第三个传感器连接到第二个FF QB',一旦QB'=1并且存在时钟下降沿,它就会改变其状态。通过这个,可以简单地产生递减计数器的计数状态。在每个第八个下降沿之后,计数器再次达到0 0 0状态。

74193递增/递减计数器

像74193这样的递增/递减计数器IC是4位的,同步递增/递减MODULO-16二进制计数器。该IC包括两个CLK输入引脚,用于对固定值进行向上计数和向下计数,因此o/p通过CLK输入同步。

单独的递增计数和递减计数端子用于更高的计数器设计或级联此递增/递减计数器IC。主复位引脚用于复位整个芯片,低电平有效并行负载i/p引脚用于开始对任何数字进行计数。

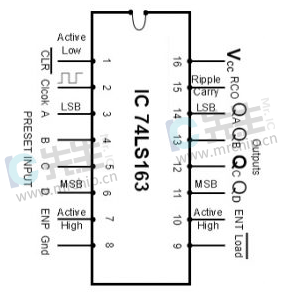

IC 74193引脚配置

IC 74193包括16个引脚,下面讨论每个引脚及其功能。

- Pin1 (CLR):这是一个低电平有效的清除i/p。

- Pin2 (CLK):这是一个时钟i/p信号。

- Pin3 (A (LSB)、Pin4(B)、Pin5 (C) 和 Pin6 (D(MSB)):这些引脚预设为i/ps以加载数据。

- Pin7 (ENP):这是一个高电平有效的i/p ENP。

- Pin8 (GND):这是接地引脚。

- Pin9(负载):这是一个低电平有效的负载i/p引脚。

- Pin10 (ENT):这是一个高电平有效的ENT i/p引脚。

- Pin11(Qd(MSB))、Pin12(Qc)、Pin13(Qb) 和 Pin14(Qa(LSB)):这些引脚是触发器的输出。

- Pin15 (RCO):这是从0–1的纹波进位o/p逻辑)。

- Pin16 (Vcc):这是电源i/p引脚。

IC 74193功能特性

74193器件主要功能特性包括以下方面内容:

- 它的CLK频率是32MHz。

- 其功耗为93mW。

- 4 位模16递增/递减计数器。

- 可获得预设i/ps。

- 它是同步可编程的。

- 内部纹波进行快速计数。

- 进行n位级联的o/p。

- 传播时间为14ns。

递增计数器和递减计数器的区别

递增计数器和递减计数器之间的区别包括以下几方面内容:

|

递增计数器

|

递减计数器 |

| 递增计数器从“0”计数到最高计数。 | 递减计数器从最高值计数到“0”值。 |

| 它按递增顺序计算事件。 | 它按降序对事件进行计数。 |

优缺点

递增/递减计数器的优点包括以下几点内容:

- 递增/递减计数器可以在高速模式下级联。

- 该计数器可以根据CLK从低到高的转换同步递增或递减。

- 很容易用触发器设计。

递增/递减计数器的缺点包括以下几点内容:

- 这些计数器没有被广泛使用,因为它们在高时钟速度下不准确。

- 对于重新同步,需要一个额外的触发器。

- 由于传播延迟,高CLK频率可能会发生计数错误。

- 这些计数器在计数大数时具有非常大的传播延迟

主要应用

递增/递减计数器的应用主要包括以下几方面内容:

- 可以用作自反转计数器。

- 可用作时钟分频器电路。

- 应用于停车场。

- 用于低噪声发射和低功耗应用。

- 可以用作分频器。

- 有助于设计异步十进制计数器。

总结

上述就是关于递增/递减计数器的相关内容概述,它是根据指定的计数输入端子的状态(高或低)选择递增-递减计数。另外,在PLC编程中,递增/递减计数器指令主要用于递增和递减计数脉冲或单位。