新闻详情

客服

STM8L050J3中文规格_功能特性_原装供应

395 2023-12-23 17:28:30 来源: 网络 作者: IC先生

概述

STM8L050J3是STM8L超低功耗8位系列的成员。

STM8L050J3具有增强的STM8 CPU核心,提供更高的处理能力(在16 MHz时高达16 MIPS),同时保持CISC架构的优势,具有改进的代码密度,24位线性寻址空间和针对低功耗操作的优化架构。

STM8L050J3 MCU包括一个集成调试模块和一个硬件接口(SWIM),允许非侵入式应用程序内调试和超快速Flash编程。

该器件集成了广泛的增强型I/ o和外设,一个12位ADC,两个比较器,一个实时时钟,两个16位定时器,一个8位定时器,以及标准通信接口,如SPI, I2C接口和一个USART。

外设的模块化设计允许该设备具有相同的外设,可以在不同的意法半导体微控制器系列中找到,包括32位系列。

STM8L050J3作为所有价值线的STM8L超低功耗产品都基于相同的架构,具有相同的内存映射和一致的引脚。

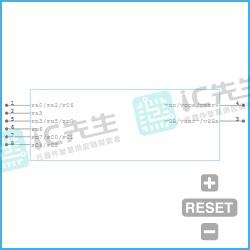

STM8L050J3符号图

STM8L050J3功能参数

- Operating conditions

- Operating power supply: 1.8 V to 3.6 V Temperature range: -40 °C to 125 °C

- Low-power features

- 5 low-power modes: Wait, Low-power run (5.1 µA), Low-power wait (3 µA), Active-halt with RTC (1.3 µA), Halt (350 nA)

- Ultra-low leakage per I/O: 50 nA

- Fast wakeup from Halt: 5 µs

- Advanced STM8 core

- Harvard architecture and 3-stage pipeline

- Max freq: 16 MHz, 16 CISC MIPS peak

- Up to 6 external interrupt sources

- Reset and supply management

- Low power, ultra-safe BOR reset with 5 selectable thresholds

- Ultra-low power POR/PDR

- Programmable voltage detector (PVD)

- Clock management

- 32 kHz and 1 to 16 MHz crystal oscillators

- Internal 16 MHz factory-trimmed RC

- Internal 38 kHz low consumption RC

- Clock security system

- Low-power RTC

- BCD calendar with alarm interrupt

- Digital calibration with +/- 0.5 ppm accuracy

- LSE security system

- Auto-wakeup from Halt w/ periodic interrupt

- Memories

- 8 Kbytes of Flash program memory and 256 bytes of data EEPROM with ECC

- Flexible write and read protection modes

- 1 Kbyte of RAM

- DMA

- 4 channels supporting ADC, SPI, I2C, USART, timers

- 1 channel for memory-to-memory

- 12-bit ADC up to 1 Msps/4 channels

- Internal reference voltage

- 计时器

- Two 16-bit timers with 2 channels (used as IC, OC, PWM), quadrature encoder

- One 8-bit timer with 7-bit prescaler

- 2 watchdogs: 1 Window, 1 Independent

- Beeper timer with 1, 2 or 4 kHz frequencies

- Communication interfaces

- Synchronous serial interface (SPI)

- Fast I2C 400 kHz SMBus and PMBus

- USART

- Up to 6 I/Os, all mappable on interrupt vectors

- Development support

- Fast on-chip programming and non-intrusive debugging with SWIM

- Bootloader using USART

- Two ultra-low-power comparators

- One with fixed threshold and another one with rail to rail

- Wakeup capability

STM8L050J3引脚图

STM8L050J3 3D图

版权声明:

部分文章信息来源于网络以及网友投稿,本网站只负责对文章进行整理、排版、编辑,是出于传递更多信息之目的,并不意味着赞同其观点或证实其内容的真实性,如本站文章和转稿涉及版权等问题,请作者及时联系本站,我们会尽快处理。

文章标签:

芯片

721次 2024-01-24 16:19:41

2408次 2024-01-03 17:20:40

1561次 2024-01-02 17:04:26

1135次 2023-12-28 17:30:12