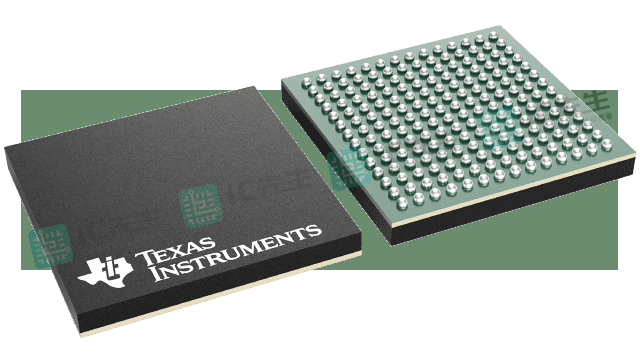

TMS320C5514规格参数_产品特点_原装现货

该器件是TI TMS320C5000™定点数字信号处理器(DSP)产品系列的成员,专为低功耗应用而设计。

定点DSP是基于TMS320C55x™DSP一代CPU处理器核心。C55x™DSP架构通过提高并行性和全面关注节能来实现高性能和低功耗。CPU支持内部总线结构,该结构由一条程序总线、一条32位数据读取总线和两条16位数据读取总线、两条16位数据写入总线以及专用于外设和DMA活动的附加总线组成。这些总线提供了在单个周期内执行最多4个16位数据读取和2个16位数据写入的能力。该设备还包括四个DMA控制器,每个控制器有4个通道,在没有CPU干预的情况下为16个独立的通道上下文提供数据移动。每个DMA控制器可以并行地独立于CPU活动,每个周期执行一个32位数据传输。

C55x CPU提供两个乘法累加(MAC)单元,每个单元能够在单个周期内进行17位x 17位乘法和32位加法。一个中央40位算术/逻辑单元(ALU)由一个额外的16位ALU支持。alu的使用在指令集控制下,提供优化并行活动和功耗的能力。这些资源在C55x CPU的AU (Address Unit)和DU (Data Unit)中进行管理。

C55x CPU支持可变字节宽度指令集,以提高代码密度。指令单元(IU)从内部或外部存储器中执行32位程序提取,并为程序单元(PU)排列指令。。预测性分支功能避免了执行条件指令时的管道刷新。

串行媒体通过两个多媒体卡/安全数字(MMC/SD)外设,四个Inter-IC Sound (I2S Bus™)模块,一个串行端口接口(SPI),最多4个芯片选择,一个I2C多主从接口和一个通用异步接收/发送器(UART)接口支持。

设备外设集包括一个外部存储器接口(EMIF),它提供对异步存储器(如EPROM、NOR、NAND和SRAM)以及高速、高密度存储器(如同步DRAM (SDRAM)和移动SDRAM (mSDRAM))的无胶合访问。。

此外,该器件还包括三个集成的ldo (DSP_LDO, ANA_LDO和USB_LDO),为器件的不同部分供电。DSP_LDO可以为DSP核心(CVDD)提供1.3 V或1.05 V,只要观察到工作频率范围,就可以通过软件实时选择。为了允许最低功耗操作,编程器可以关闭内部DSP_LDO切割电源到DSP核心(CVDD),而外部电源为RTC (CVDDRTC和DVDDRTC)提供电源。。。

该设备由业界屡获殊荣的eXpressDSP™、Code Composer Studio™集成开发环境(IDE)、DSP/BIOS™、德州仪器的算法标准以及业界最大的第三方网络支持。Code Composer Studio IDE具有代码生成工具,包括C编译器和链接器,RTDX™,XDS100™,XDS510™,XDS560™仿真设备驱动程序和评估模块。该器件还支持C55x DSP库,该库具有50多个基础软件内核(FIR滤波器,IIR滤波器和各种数学函数)以及芯片支持库。

TMS320C5514的特性

- High-Performance, Low-Power, TMS320C55x™ Fixed-Point Digital Signal Processor

- 16.67-, 13.33-, 10-, 8.33-ns指令周期时间

- 时钟频率:60、75、100、120 mhz

- 每周期执行一条/两条指令

- 双乘数[每秒最多2亿或2.4亿次乘数累积]

- 两个算术/逻辑单元(alu)

- 三个内部数据/操作数读总线和两个内部数据/操作数写总线

- 软件兼容C55x设备

- 工业温度设备

- 256K字节零等待状态片上RAM,由:

- 64K Bytes of Dual-Access RAM (DARAM), 8 Blocks of 4K x 16-Bit

- 192K字节的单访问RAM (SARAM), 24块4K x 16位

- 128K字节的零等待状态片上ROM

(4块16K x 16位) - 最大16位可寻址外部内存空间(SDRAM/mSDRAM)

- 16-/8位外部存储器接口(EMIF),无胶接口:

- 8位/16位NAND闪存,1位和4位ECC

- 8-/16位NOR Flash

- 异步静态内存(SRAM)

- SDRAM/mSDRAM (1.8 v, 2.5 v, 2.75 v和3.3 v)

- 直接内存访问(DMA)控制器

- 4个DMA各4通道(共16通道)

- 三个32位通用定时器

- 一个可选作为看门狗和/或GP

- 两个多媒体卡/安全数字(MMC/SD)接口

- 通用异步收发器(UART)

- 串行端口接口(SPI)与四个芯片选择

- 主从间集成电路(12C Bus™)

- 四种内音(一2S Bus™) for Data Transport

- 设备USB接口集成2.0高速PHY,支持:

- USB 2.0全高速设备

- 实时时钟(RTC)与晶体输入,具有独立的时钟域和电源

- 四核隔离电源领域:模拟,RTC, CPU和外设,和USB

- 4个I/O隔离供电域:RTC I/O、EMIF I/O、USB PHY、DVDDIO

- 3个集成ldo (DSP_LDO、ANA_LDO、USB_LDO)为隔离域供电,分别为DSP Core、Analog、USB Core

- 低功耗S/W可编程锁相环(PLL)时钟发生器

- 片上ROM引导加载程序(RBL)从NAND闪存,NOR闪存,SPI EEPROM, SPI串行闪存或I2C EEPROM启动

- ieee - 1149.1 (JTAG)

Boundary-Scan-Compatible - 多达26个通用I/O (GPIO)引脚

(与其他设备功能复用) - 196端子无铅塑料BGA(球栅阵列)(ZCH后缀)

- 1.05 v核心(60或75 MHz), 1.8 v, 2.5 v, 2.75 v或3.3 v I/ o

- 1.3 v核心(100,120mhz), 1.8 v, 2.5 v, 2.75 v或3.3 v I/ o

所有商标均为其各自所有者的财产。

TMS320C5514功能图

TMS320C5514规格参数

| 产品属性 | 属性值 |

|---|---|

| DSP类型 | 1 C55x |

| DSP (max) (MHz) | 100, 120 |

| CPU | 16-bit |

| 操作系统 | DSP/BIOS, VLX |

| 评级 | Catalog |

| 工作温度范围(℃) | -40 to 85, 0 to 0 |